# **3.3V Single Channel Video Driver with Recontruction Filter and SAG Correction**

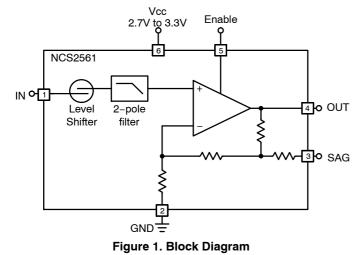

The NCS2561 is a single high speed video driver including a 2-pole reconstruction filter and SAG correction capability. The NCS2561 is available in a space saving SC-88 package optimized for low voltage, portable applications. It is designed to be compatible with Digital-to-Analog Converters (DAC) embedded in most video processors.

The NCS2561 internally integrates an 8 MHz 2-pole video DAC reconstruction filter with a fixed gain of 2. The NCS2561 also has a built-in SAG correction circuit when used at the output in an AC-coupled mode. To further reduce power consumption, an enable pin is provided.

## Features

- Internal 8 MHz 2-Pole Reconstruction Filter

- Internal Fixed Gain: 6 dB

- Integrated Level Shifter

- SAG Correction Circuit for Reducing Coupling Capacitor Size

- Low Quiescent Current: 6 mA Typ

- Shutdown Current <  $5 \mu A$

- Wide Input Voltage Range

- Capability to Drive 2 CVBS Video Signals Together (2x150Ω Loads)

- Excellent Video Performance

- Operating Supply Voltage Range: +2.7 V to +3.3 V

- Space-Saving SC-88 Package

- Pin-Compatible with Similar Competitive Devices

- This is a Pb–Free Device

## Applications

- Portable Video

- Digital Cameras

- Camera Phones

- Set-Top Box Video Filters

- NTSC and PAL

ON

# **ON Semiconductor®**

http://onsemi.com

YG1 = Specific Device Code M = Date Code\* • = Pb-Free Package

(Note: Microdot may be in either location)

\*Date Code orientation and/or position may vary depending upon manufacturing location.

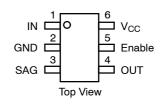

## PIN CONNECTIONS

## ORDERING INFORMATION

| Device       | Package            | Shipping <sup>†</sup> |

|--------------|--------------------|-----------------------|

| NCS2561SQT1G | SC-88<br>(Pb-Free) | 3000 / Tape & Reel    |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

### **Related Resource:**

Refer to Application Note AND8457/D for details regarding SAG Correction

## PIN FUNCTION AND DESCRIPTION

| Pin | Name            | Туре   | Description                                                                                        |

|-----|-----------------|--------|----------------------------------------------------------------------------------------------------|

| 1   | IN              | Input  | Video Input                                                                                        |

| 2   | GND             | Ground | Ground                                                                                             |

| 3   | SAG             | Output | Sag Compensation                                                                                   |

| 4   | OUT             | Output | Video Output                                                                                       |

| 5   | Enable          | Input  | Enable / Disable Function: High = Enable, Low = Disable. When left open the default state is High. |

| 6   | V <sub>CC</sub> | Power  | Power Supply / 2.7 V < $V_{CC}$ < 3.3 V                                                            |

### ATTRIBUTES

|                   | Characteristic                                                 | Value                |

|-------------------|----------------------------------------------------------------|----------------------|

| ESD Protection    | Human Body Model, R = 1000 $\Omega$ , C = 100 pF Machine Model | 2 kV<br>200 V        |

| Moisture Sensitiv | ty (Note 1)                                                    | Level 1              |

| Flammability Rati | ng Oxygen Index: 28 to 34                                      | UL 94 V–0 @ 0.125 in |

1. For additional Moisture Sensitivity information, refer to Application Note AND8003/D.

## MAXIMUM RATINGS

| Rating                                       | Symbol           | Value                         | Unit |

|----------------------------------------------|------------------|-------------------------------|------|

| Power Supply Voltages                        | V <sub>CC</sub>  | 3.6                           | Vdc  |

| Input Voltage Range                          | VI               | –0.5 to V <sub>CC</sub> + 0.5 | Vdc  |

| Output Short–Circuit to GND thru 75 $\Omega$ | I <sub>SC</sub>  | Continuous                    | _    |

| Maximum Junction Temperature (Note 2)        | TJ               | 150                           | °C   |

| Operating Ambient Temperature                | T <sub>A</sub>   | -40 to +125                   | °C   |

| Storage Temperature Range                    | T <sub>stg</sub> | –60 to +150                   | °C   |

| Thermal Resistance, Junction-to-Air          | $R_{\thetaJA}$   | 250                           | °C/W |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

2. Power dissipation must be considered to ensure maximum junction temperature (T<sub>J</sub>) is not exceeded.

## MAXIMUM POWER DISSIPATION

The maximum power that can be safely dissipated is limited by the associated rise in junction temperature. For the plastic packages, the maximum safe junction temperature is 150°C. If the maximum is exceeded momentarily, proper circuit operation will be restored as soon as the die temperature is reduced. Leaving the device in the "overheated" condition for an extended period can result in device burnout. To ensure proper operation, it is important to observe the de-rating curves.

| Symbol           | Characteristic                                                               | Conditions                                                                                  | Min                   | Тур                                            | Max                   | Unit |

|------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------|-----------------------|------|

| DC PERF          | ORMANCE                                                                      |                                                                                             |                       |                                                |                       |      |

| V <sub>OLS</sub> | Offset Level–Shift Output Voltage<br>$T_A = -40^{\circ}C$ to +125°C (Note 3) | $V_{CC}$ = 3.3 V, $V_{IN}$ = 0 V                                                            | 10                    | 60<br>60                                       | 80                    | mV   |

| I <sub>IB</sub>  | Input Bias Current                                                           |                                                                                             |                       | ±3                                             |                       | pА   |

| V <sub>IN</sub>  | Input Voltage Range (Note 4)                                                 | V <sub>CC</sub> = 3.3 V                                                                     | GND                   |                                                | V <sub>CC</sub> – 1.5 | V    |

| A <sub>V</sub>   | Voltage Gain                                                                 | V <sub>CC</sub> = 3.3 V, 0 < V <sub>IN</sub> < 1.5 V<br>40 IRE Sync,<br>100 IRE White Level | 5.8                   | 6.0                                            | 6.2                   | dB   |

| V <sub>IH</sub>  | Enable Input High Level Voltage                                              |                                                                                             | 1.6                   |                                                | V <sub>CC</sub>       | V    |

| V <sub>IL</sub>  | Enable Input Low Level Voltage                                               |                                                                                             | GND                   |                                                | 0.8                   | V    |

| OUTPUT           | CHARACTERISTICS                                                              |                                                                                             |                       |                                                |                       |      |

| V <sub>OH</sub>  | Output High Level Voltage                                                    | $R_L$ = 150 Ω to GND<br>$R_L$ = 75 Ω to GND                                                 | V <sub>CC</sub> – 0.3 | V <sub>CC</sub> - 0.1<br>V <sub>CC</sub> - 0.3 |                       | V    |

| V <sub>OL</sub>  | Output Low Level Voltage<br>(Note 5)                                         |                                                                                             |                       | 60                                             |                       | mV   |

#### POWER SUPPLY

$I_0$

| V <sub>CC</sub>         | Operating Voltage Range                                                   |                                                  | 2.7 |     | 3.3        | V    |

|-------------------------|---------------------------------------------------------------------------|--------------------------------------------------|-----|-----|------------|------|

| I <sub>CC, ON</sub>     | Power Supply Current – Enabled<br>$T_A = -40^{\circ}C$ to +125°C (Note 3) | $V_{IN}$ = 0 V, $V_{CC}$ = 3.3 V, $I_{O}$ = 0 mA |     | 6.0 | 7.5<br>9.0 | mA   |

| I <sub>CC,</sub><br>OFF | Power Supply Current – Disabled                                           | $V_{IN}$ = 0 V, $V_{CC}$ = 3.3 V, $I_{O}$ = 0 mA |     | 1.5 | 5.0        | μΑ   |

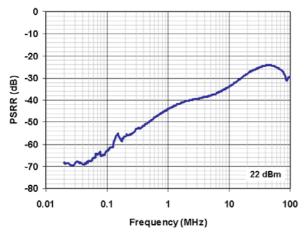

| PSRR                    | Power Supply Rejection Ratio                                              | $V_{CC}$ = 2.7 V to 3.3 V                        |     | ±80 |            | μV/V |

$V_{CC} = 3.3 \overline{V}$

±50

mΑ

3. Guaranteed by design and/or characterization.

**Output Current**

Limited by output swing and internal gain.

Output low voltage level is limited by the internal level shift circuitry.

## AC ELECTRICAL CHARACTERISTICS with V<sub>CC</sub> = 2.7 V to 3.3 V (T<sub>A</sub> = +25°C, R<sub>L</sub> = 150 $\Omega$ to GND, unless otherwise specified)

| Symbol       | Characteristic                       | Conditions                                                                                                                                                                                                                                                                                                      | Min                 | Тур              | Max          | Unit |  |  |  |

|--------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------|--------------|------|--|--|--|

| FREQUE       | FREQUENCY DOMAIN PERFORMANCE         |                                                                                                                                                                                                                                                                                                                 |                     |                  |              |      |  |  |  |

| An           | Normalized Passband Gain (Note<br>6) | $ \begin{array}{l} {\sf V}_{CC}{=}3.3 \; {\sf V},  {\sf f}{=}1.0 \; {\sf MHz} \;,  {\sf V}_{O}{=}2 \; {\sf V}_{p-p} \\ {\sf V}_{CC}{=}3.3 \; {\sf V},  {\sf f}{=}4.5 \; {\sf MHz} \;,  {\sf V}_{O}{=}2 \; {\sf V}_{p-p} \\ {\sf f}{=} \; 27 \; {\sf MHz}, \; {\sf V}_{O}{=} \; 2 \; {\sf V}_{p-p} \end{array} $ | -0.4<br>-0.2<br>-18 | 0<br>+0.4<br>-22 | +0.4<br>+0.8 | dB   |  |  |  |

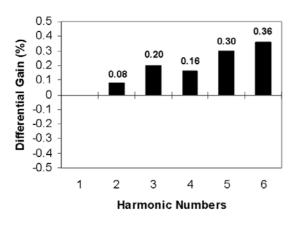

| dG           | Differential Gain                    | $\label{eq:V_{CC}} \begin{array}{l} {\sf V}_{CC} = 3.3 \; {\sf V},  {\sf A}_{V} = +2,  {\sf R}_{L} = 150 \; \Omega, \\ {\sf f} = 3.58 \; {\sf MHz},  4.43 \; {\sf MHz} \end{array}$                                                                                                                             |                     | 0.5              |              | %    |  |  |  |

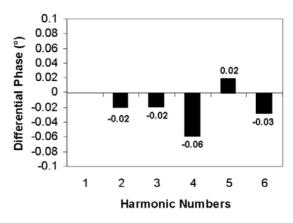

| dP           | Differential Phase                   | $\label{eq:V_{CC}} \begin{array}{l} {\sf V}_{CC} = 3.3 \; {\sf V},  {\sf A}_{V} = +2,  {\sf R}_{L} = 150 \; \Omega, \\ {\sf f} = 3.58 \; {\sf MHz},  4.43 \; {\sf MHz} \end{array}$                                                                                                                             |                     | 1.0              |              | 0    |  |  |  |

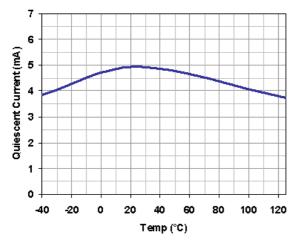

| SNR          | Signal to Noise Ratio                | $V_{CC}$ = 3.3 V, 100% White Signal                                                                                                                                                                                                                                                                             |                     | 70               |              | dB   |  |  |  |

| TIME DO      | MAIN RESPONSE                        |                                                                                                                                                                                                                                                                                                                 |                     |                  |              |      |  |  |  |

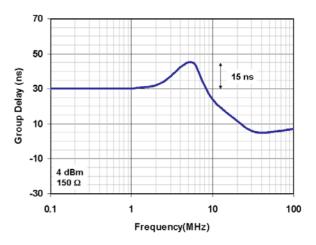

| $\Delta T_g$ | Group Delay Variation                | $V_{CC}$ = 3.3 V, 100 kHz to 5.0 MHz                                                                                                                                                                                                                                                                            |                     | 15               |              | ns   |  |  |  |

| $\Delta T_g$     | Group Delay Variation | $V_{CC}$ = 3.3 V, 100 kHz to 5.0 MHz | 15  | ns |

|------------------|-----------------------|--------------------------------------|-----|----|

| t <sub>ON</sub>  | Turn ON Time          |                                      | 1.5 | μs |

| t <sub>OFF</sub> | Turn OFF Time         |                                      | 50  | ns |

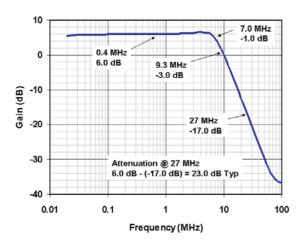

6. The normalized gain is guaranteed by design and characterization. The max normalized gain of +0.8 dB is the result of smooth peaking (pre-emphasis, see figure 2) taking into account the increase of the losses at the highest frequencies into connectors and cable at the output. For frequencies lower than 2 MHz the max normalized gain is 0.4 dB.

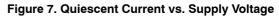

TYPICAL CHARACTERISTICS (At  $T_A$  = +25°C and  $R_L$  = 150  $\Omega\!,$  unless otherwise specified)

Figure 2. Frequency Response

Figure 3. Group Delay vs. Frequency

Figure 4. Differential Gain

Figure 5. Differential Phase

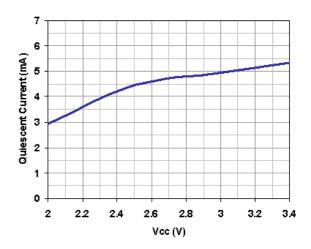

Figure 8. Quiescent Current vs. Temperature ( $V_{CC}$  = 3.0 V)

Figure 9. Signal-to-Noise Ratio vs. Temperature

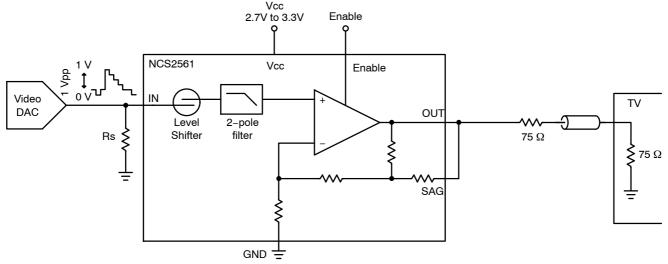

## **APPLICATIONS INFORMATION**

The NCS2561 is a single video driver optimized for portable applications with low power consumption in a space saving SC-88 package. It includes sag correction circuitry allowing significant reduction of the AC-coupled output capacitor.

## **Internal Level Shift**

The input common mode voltage range (see specifications  $V_{IN}$ ) of the NCS2561 includes the lower rail (GND) and extends to  $V_{CC}$  – 1.5V on a power supply range of 2.7 V to 3.3 V. Many video processors operate with a supply ranging from 0 V to a positive supply (typically 3.3 V), so the lowest voltage of the video signal provided by the DAC is 0 V. Although a 0 V (GND) signal is within the input common-mode range of the NCS2561, the output signal will be limited, specifically at the lower rail. Op amps use transistors with saturation voltage (Vsat) higher than 0 V. If the lowest level of the input voltage is lower than Vsat the signal will be clipped at the output.

To ensure the output signal is not clipped due to the lower rail limit, the NCS2561 has built–in level shift circuitry. The role of this circuitry is to avoid clipping of the sync signal at the output by shifting up the video signal by about 60 mV. The level shift circuitry level shifts the sync signal above the internal op amp transistor saturation limit. This function is particularly useful when the video signal is DC–coupled at the output.

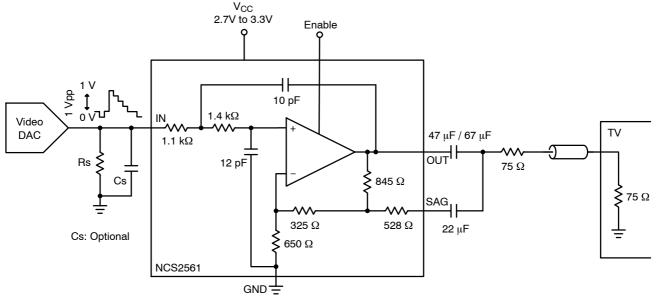

### **Built-in 2-Pole Reconstruction Filter**

The NCS2561 has a 2-pole reconstruction filter with a -3 dB cut-off frequency at 8 MHz. The filter serves as an anti-alias filter removing the unwanted over-sampling effects produced by the video DAC. The 27 MHz over-sampling frequency from the video DAC is attenuated by 22 dB typical. In order to improve the stop-band attenuation a small capacitor (Cs) of a few tenths pico Farads can be added in parallel with the source resistor (Rs) (See Figure 10).

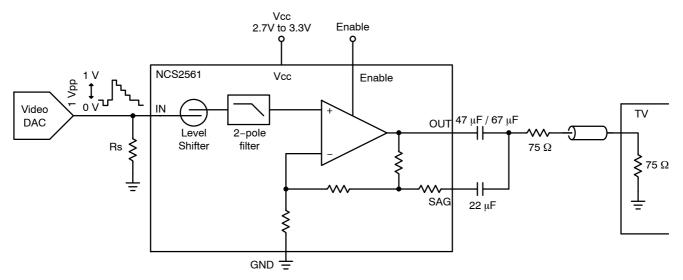

Figure 10. Block Diagram Showing Filter and Sag Correction Circuits

## Shutdown Mode

If the Enable pin is left open by default the circuit will be enabled. The Enable pin offers a shutdown function, so the NCS2561 can consequently be disabled when not used. This is particularly important for digital still cameras or cell phones with camera having a video output feature. Indeed this video output is not permanently used and actually used in very specific period of time when pictures or small movies want to be displayed on a bigger screen. The device's quiescent current drops typically down to 2.7  $\mu$ A when the device is in the shutdown mode.

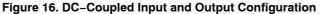

## Sag Correction

Video drivers that do not incorporate sag compensation traditionally recommend a large coupling capacitor (220  $\mu$ F) on the output of the video driver. Larger output coupling capacitors ( $\geq$  470  $\mu$ F) are often chosen by design engineers when the application allows this (Set–Top Box). A larger output coupling capacitor allows a lower cut–off frequency to avoid field tilt effects; however in portable applications there is a trade–off between large and expensive coupling

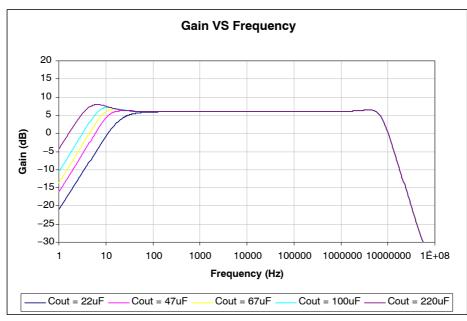

capacitors, and a coupling configuration to saving space. The sag compensation circuitry allows the reduction of this output coupling capacitor value by inducing peaking at the lower cutoff frequency of the high pass filter. The high-pass filter is created by the coupling capacitor and the load resistor (1/( $2\pi R_L$ Cout), and this peaking lowers the cutoff frequency. Simulation results provided in Figure 11 show the effect of the sag compensation at the low cut-off frequency.

Figure 11. Simulation Results with Csag =  $22 \mu$ F and Variable Cout

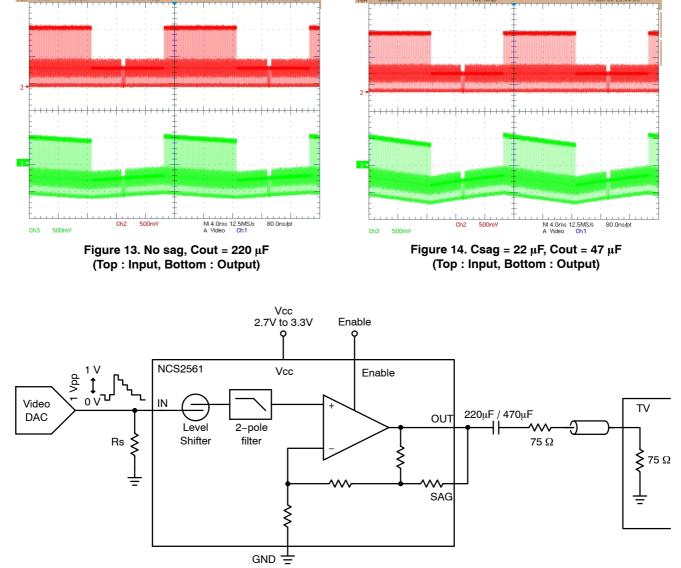

Calculations show that a 220  $\mu$ F output capacitor produces a low cutoff frequency of 5 Hz, and a 470  $\mu$ F capacitor will give a low cutoff frequency at 2.6 Hz. The cutoff frequency (-3 dB) is defined by the equation:  $1/(2\pi R_L Cout)$ . In the case where no sag is used (Figure 14), a low Cout value can adversely affect the low cutoff frequency; the cut–off frequency will be in the critical 50 Hz or 60 Hz frequencies. This undesirable affect will manifest itself as field tilt. Due to the SAG correction the large output capacitor is reduced without degrading the video performances by the use of two smaller and cheaper output capacitors.

Figure 12. Sag Correction Configuration

The Csag value has no significant impact on the coupling even as the value increases. A value of 22  $\mu$ F is recommended for optimal performance.

To achieve similar behavior to an output coupling capacitor value Cout = 220  $\mu$ F (no sag) the nominal equivalent sag combination is Csag = 22  $\mu$ F and Cout = 67  $\mu$ F. A value of 47  $\mu$ F for Cout will yield equivalent results. If we consider a coupling cap of 470  $\mu$ F, the best compromise for sag combination is Csag = 22  $\mu$ F and Cout = 100  $\mu$ F. A value of 67  $\mu$ F for Cout will yield equivalent results.

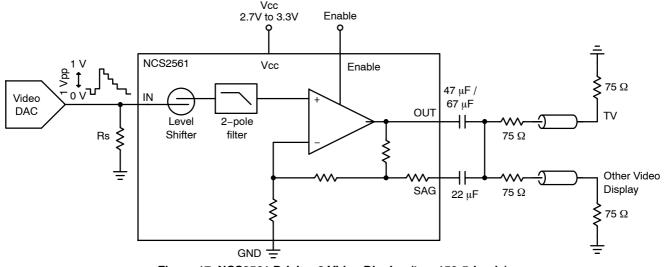

Figures 13 and 14 show the impact of the output coupling capacitor on a video signal corresponding to a worst case situation regarding the low frequency bandwidth. The video signal used is a 50 Hz 1/2 black – 1/2 white video pattern. This signal is obtained using the PAL Flat Field Square wave signal option available with the video generator TG700 from Tektronix. These measurements show how the sag function can help to reduce the field tilt problem using lower value coupling capacitor than traditional approach.

## **DC–Coupled Output**

Having efficient output AC-coupled capability thanks to the sag correction option, with the built-in level shifter, the NCS2561 can also be DC-coupled to a 150  $\Omega$  load. This has the advantage of eliminating the AC-coupling capacitors at the output by reducing the number of external components and saving space on the board. This can be a key advantage for some portable applications with limited space. The problems of field tilt effects on the video signal are also eliminated providing the best video quality with optimal dynamic or peak-to-peak amplitude of the video signal allowing operating at the lower power supply voltage (2.7 V) without risk of signal clipping. In this coupling configuration the average output voltage is higher than 0 V and the power consumption can be a little higher than with an AC-coupled configuration.

## Video Driving Capability

With an output current capability of  $\pm 50$  mA the NSC2561 was designed to be able to drive at least 2 video display loads in parallel (2 different display or 1 display + 1 VCR). This

applications is illustrated in the Figure 17. Figure 18 (multiburst) and Figure 19 (linearity) show that the video signal can efficiently drive a 75  $\Omega$  equivalent load and not degrade the video performance.

Figure 17. NCS2561 Driving 2 Video Display (two 150  $\Omega$  loads)

Figure 18. Multiburst Test with two 150  $\Omega$  loads

## **ESD** Protection

All the device pins are protected against electrostatic discharge at a level of 2 kV HBM. The output has been considered with a particular attention with ESD structure able to sustain typically more than 2 kV HBM. Actually

Figure 19. Linearity Test with two 150  $\Omega$  loads

more than 4 kV has been measured on this specific output pin. This feature is particularly important for video driver which usually constitutes the last stage in the video chain before the video output connector.

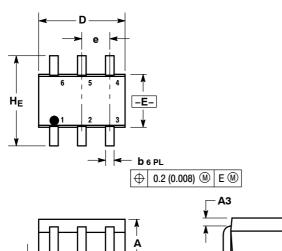

#### PACKAGE DIMENSIONS

SC-88/SC70-6/SOT-363 CASE 419B-02 ISSUE W

NOTES: 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. 419B-01 OBSOLETE, NEW STANDARD 419B-02.

|     | MILLIMETERS |          |      | INCHES    |         |       |

|-----|-------------|----------|------|-----------|---------|-------|

| DIM | MIN         | NOM      | MAX  | MIN       | NOM     | MAX   |

| Α   | 0.80        | 0.95     | 1.10 | 0.031     | 0.037   | 0.043 |

| A1  | 0.00        | 0.05     | 0.10 | 0.000     | 0.002   | 0.004 |

| A3  |             | 0.20 RE  | F    | 0.008 REF |         |       |

| b   | 0.10        | 0.21     | 0.30 | 0.004     | 0.008   | 0.012 |

| С   | 0.10        | 0.14     | 0.25 | 0.004     | 0.005   | 0.010 |

| D   | 1.80        | 2.00     | 2.20 | 0.070     | 0.078   | 0.086 |

| Е   | 1.15        | 1.25     | 1.35 | 0.045     | 0.049   | 0.053 |

| е   | (           | 0.65 BSC |      | 0         | .026 BS | С     |

| L   | 0.10        | 0.20     | 0.30 | 0.004     | 0.008   | 0.012 |

| HE  | 2.00        | 2.10     | 2.20 | 0.078     | 0.082   | 0.086 |

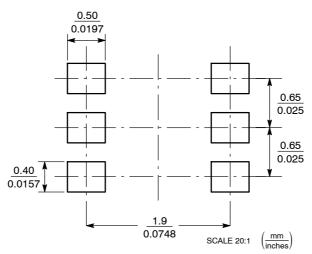

#### SOLDERING FOOTPRINT\*

н

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and use registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death agsociated with such unintended or unauthorized use payers that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunit//Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

Δ1

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5773-3850 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative